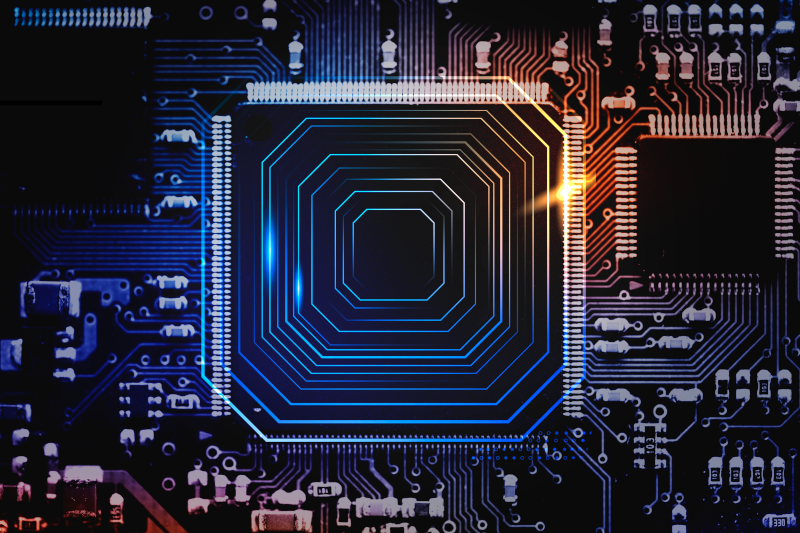

T1 is a RISC-V Cray

The crux of most supercomputers is the ability to operate on many pieces of data at once — something video cards are good at, too. Enter T1 (short for Torrent-1), …read more

The crux of most supercomputers is the ability to operate on many pieces of data at once — something video cards are good at, too. Enter T1 (short for Torrent-1), a RISC-V vector inspired by the Cray X1 vector machine.

T1 has support for features, including lanes and chaining. The chip contains a version of the Rocket Core for scalar operations, but there’s no official support for using it. The project claims you could easily replace that core with any other RISC-V CPU IP.

By focusing on parallelism instead of out of order execution, the design gets to skip branch prediction, register renaming, and similar problems.

There is an emulator if you want to experiment. You can even grab a docker image for easy installation. This doesn’t look like something you could pick up in an hour, so prepare to spend some time. Everything is bare-metal, too, so leave your favorite development tools at home.

The project uses Chisel, which we’ve covered before. The build system seems very complex, but based on Nix Flakes, so it should be understandable.

If your high-performance RISC-V dreams are more conventional, there’s work going on in that area, too.

Title graphic from Freepik.

_Igor_Stevanovic_Alamy_Stock_Photo.jpg?#)